# System Manual PLCcore-9G20

# User Manual Version 1.0

# **Edition July 2010**

Document No.: L-1254e\_1

SYS TEC electronic GmbH August-Bebel-Str. 29 D-07973 Greiz Phone: +49 (3661) 6279-0 Fax: +49 (3661) 6279-99 Web: http://www.systec-electronic.com Mail: info@systec-electronic.com

SYS TEC electronic GmbH - System House for distributed Automation

# Status/Changes

Status: released

| Date/Version      | Section | Changes  | Editor    |

|-------------------|---------|----------|-----------|

| 2010/07/15<br>1.0 | All     | Creation | R. Sieber |

|                   |         |          |           |

|                   |         |          |           |

|                   |         |          |           |

|                   |         |          |           |

|                   |         |          |           |

|                   |         |          |           |

|                   |         |          |           |

|                   |         |          |           |

|                   |         |          |           |

|                   |         |          |           |

|                   |         |          |           |

|                   |         |          |           |

|                   |         |          |           |

|                   |         |          |           |

| © SYS TEC electronic GmbH 2010 | L-1254e 1 | Page 1  |  |

|--------------------------------|-----------|---------|--|

|                                |           | i ugo i |  |

This manual includes descriptions for copyrighted products that are not explicitly indicated as such. The absence of the trademark (©) symbol does not infer that a product is not protected. Additionally, registered patents and trademarks are similarly not expressly indicated in this manual.

The information in this document has been carefully checked and is believed to be entirely reliable. However, SYS TEC electronic GmbH assumes no responsibility for any inaccuracies. SYS TEC electronic GmbH neither guarantees nor accepts any liability whatsoever for consequential damages resulting from the use of this manual or its associated product. SYS TEC electronic GmbH reserves the right to alter the information contained herein without prior notification and does not accept responsibility for any damages which might result.

Additionally, SYS TEC electronic GmbH neither guarantees nor assumes any liability for damages arising from the improper usage or improper installation of the hardware or software. SYS TEC electronic GmbH further reserves the right to alter the layout and/or design of the hardware without prior notification and accepts no liability for doing so.

© Copyright 2010 SYS TEC electronic GmbH. All rights – including those of translation, reprint, broadcast, photomechanical or similar reproduction and storage or processing in computer systems, in whole or in part – are reserved. No reproduction may occur without the express written consent from SYS TEC electronic GmbH.

| Contact                  | Direct                                                                      | Your local distributor                            |

|--------------------------|-----------------------------------------------------------------------------|---------------------------------------------------|

| Address:                 | SYS TEC electronic GmbH<br>August-Bebel-Str. 29<br>D-07973 Greiz<br>GERMANY |                                                   |

| Ordering<br>Information: | +49 (0) 36 61 / 62 79-0<br>info@systec-electronic.com                       | Please find a list of our<br>distributors under:  |

| Technical Support:       | +49 (0) 36 61 / 62 79-0<br>support@systec-electronic.com                    | http://www.systec-<br>electronic.com/distributors |

| Fax:                     | +49 (0) 36 61 / 6 79 99                                                     |                                                   |

| Web Site:                | http://www.systec-electronic.com                                            |                                                   |

Inform yourselves:

1st Edition July 2010

# **Table of Contents**

| 1 | Intro       | duction                                                                             | 5    |

|---|-------------|-------------------------------------------------------------------------------------|------|

| 2 | Over        | view / Where to find what?                                                          | 6    |

| 3 | Prod        | uct Description                                                                     | 8    |

|   | <b>D</b>    |                                                                                     | 40   |

| 4 | <b>Deve</b> | elopment Kit PLCcore-9G20                                                           |      |

|   | 4.1<br>4.2  | Electric commissioning of the Development Kit PLCcore-9G20                          |      |

|   | 4.3         | Control elements of the Development Kit PLCcore-9G20                                |      |

|   | 4.4         | Optional accessory                                                                  |      |

|   |             | 4.4.1 USB-RS232 Adapter Cable                                                       | . 13 |

|   |             | 4.4.2 Driver Development Kit (DDK)                                                  |      |

| 5 | Pino        | ut of the PLCcore-9G20                                                              | .14  |

| 6 | PLC         | Functionality of the PLCcore-9G20                                                   | .17  |

| • | 6.1         | Overview                                                                            |      |

|   | 6.2         | System start of the PLCcore-9G20                                                    |      |

|   | 6.3         | Programming the PLCcore-9G20                                                        | . 18 |

|   | 6.4         | Process image of the PLCcore-9G20                                                   |      |

|   |             | 6.4.1 Local In- and Outputs                                                         |      |

|   |             | 6.4.2 In- and outputs of user-specific baseboards                                   |      |

|   | 6.5         | Communication interfaces                                                            |      |

|   |             | 6.5.1 Serial interfaces                                                             |      |

|   |             | <ul><li>6.5.2 CAN interfaces</li><li>6.5.3 Ethernet interfaces</li></ul>            |      |

|   | 6.6         | 6.5.3 Ethernet interfaces<br>Specific peripheral interfaces                         |      |

|   | 0.0         | 6.6.1 Counter inputs                                                                |      |

|   |             | 6.6.2 Pulse outputs                                                                 |      |

|   | 6.7         | Control and display elements                                                        |      |

|   | -           | 6.7.1 Run/Stop switch                                                               |      |

|   |             | 6.7.2 Run-LED (green)                                                               | . 22 |

|   |             | 6.7.3 Error-LED (red)                                                               |      |

|   | 6.8         | Local deletion of a PLC program                                                     |      |

|   | 6.9         | Using CANopen for CAN interfaces                                                    |      |

|   |             | 6.9.1 CAN interface CAN0                                                            |      |

|   |             | 6.9.2 Additional CAN interfaces                                                     | . 26 |

| 7 |             | iguration and Administration of the PLCcore-9G20                                    |      |

|   | 7.1         | System requirements and necessary software tools                                    |      |

|   | 7.2<br>7.3  | Activation/Deactivation of Linux Autostart                                          |      |

|   | 7.3<br>7.4  | Ethernet configuration of the PLCcore-9G20<br>PLC configuration of the PLCcore-9G20 |      |

|   | 7.4         | 7.4.1 PLC configuration via WEB-Frontend                                            |      |

|   |             | 7.4.2 PLC configuration via control elements of the Development Kit PLCcore-9G20    |      |

|   |             | 7.4.3 Setup of the configuration file "plccore-9g20.cfg"                            |      |

|   | 7.5         | Boot configuration of the PLCcore-9G20                                              |      |

|   | 7.6         | Selecting the appropriate firmware version                                          |      |

|   | 7.7         | Predefined user accounts                                                            | . 37 |

|   | 7.8         | Login to the PLCcore-9G20                                                           |      |

|   |             | 7.8.1 Login to the command shell                                                    |      |

|   |             | 7.8.2 Login to the FTP server                                                       |      |

|   | 7.9         | Adding and deleting user accounts                                                   |      |

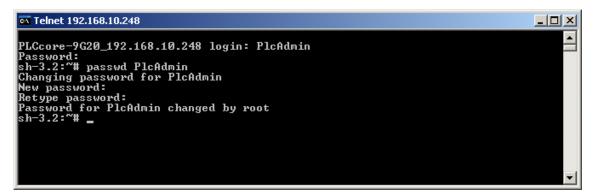

|   | 7.10        | How to change the password for user accounts                                        |      |

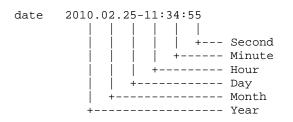

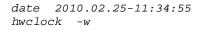

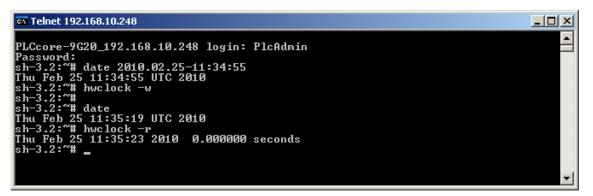

|   | 7.11        | Setting the system time                                                             | . 41 |

|     | 7.12   | File system of the PLCcore-9G20                   | 42 |

|-----|--------|---------------------------------------------------|----|

|     | 7.13   | Software update of the PLCcore-9G20               | 43 |

|     |        | 7.13.1 Updating the PLC firmware                  | 43 |

|     |        | 7.13.2 How to update the Linux-Image              | 45 |

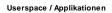

| 8   | Adap   | otion of In-/Outputs and Process Image            | 48 |

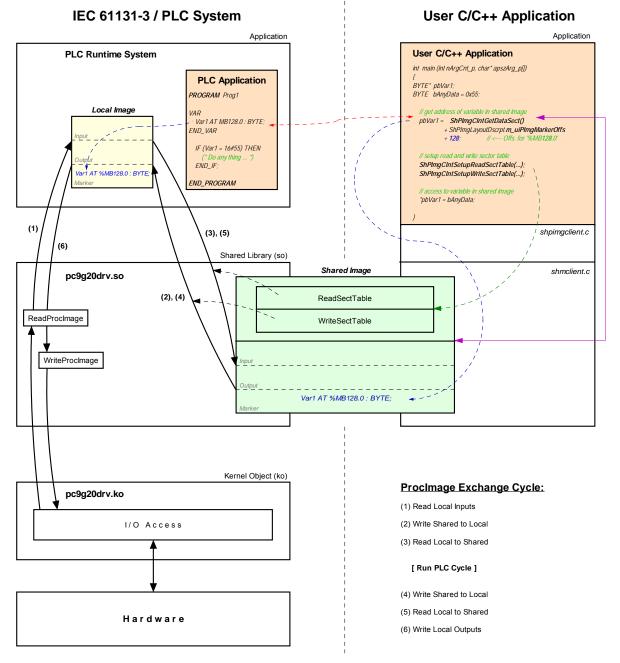

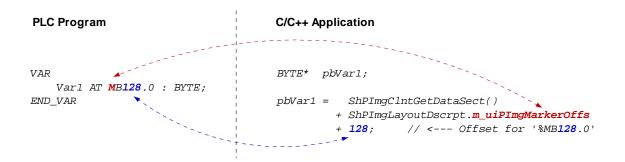

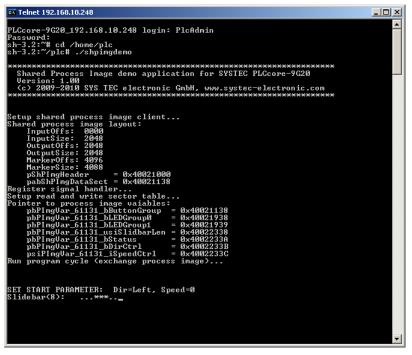

|     | 8.1    | Data exchange via shared process image            | 48 |

|     |        | 8.1.1 Overview of the shared process image        |    |

|     |        | 8.1.2 API of the shared process image client      |    |

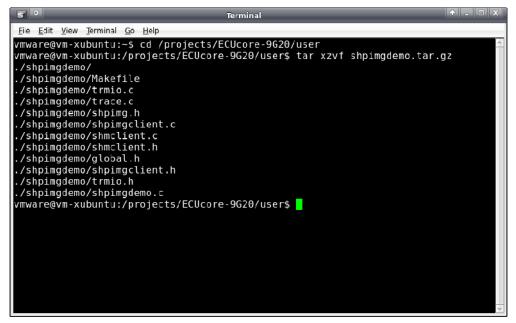

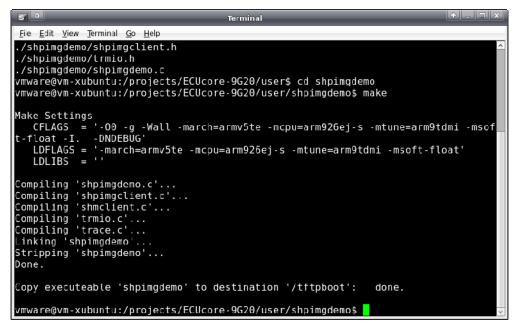

|     |        | 8.1.3 Creating a user-specific client application |    |

|     |        | 8.1.4 Example for using the shared process image  |    |

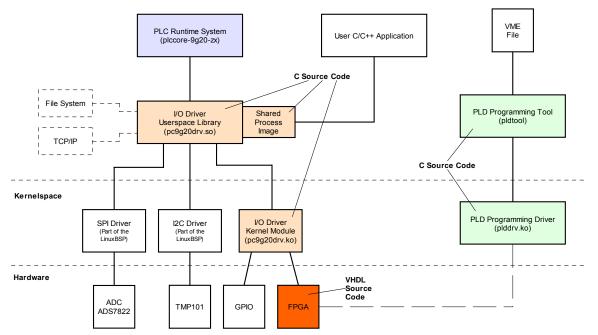

|     | 8.2    | Driver Development Kit (DDK) for the PLCcore-9G20 |    |

|     | 8.3    | Testing the hardware connections                  | 63 |

| Арр | pendix | x A: Firmware function scope of PLCcore-9G20      | 64 |

| Арр | bendix | x B: Reference design for the PLCcore-9G20        | 67 |

| Арр | bendix | x C: GNU GENERAL PUBLIC LICENSE                   | 70 |

| Ind | ex     |                                                   | 75 |

| © SYS TEC electronic GmbH 2010 | L-1254e_1 | Page 4 |

|--------------------------------|-----------|--------|

|--------------------------------|-----------|--------|

# 1 Introduction

Thank you that you have decided for the SYS TEC PLCcore-9G20. This product provides to you an innovative and high-capacity PLC-kernel. Due to its high performance on a small manufactured size and due to its low power consumption, it is well-suitable as communication and control processor for embedded applications.

Please take some time to read through this manual carefully. It contains important information about the commissioning, configuration and programming of the PLCcore-9G20. It will assist you in getting familiar with the functional range and usage of the PLCcore-9G20. This document is complemented by other manuals, e.g. for the *OpenPCS* IEC 61131 programming system and the CANopen extension for IEC 61131-3. Table 3 in section 4.1 shows a listing of relevant manuals for the PLCcore-9G20. Please also refer to those complementary documents.

For more information, optional products, updates et cetera, we recommend you to visit our website: <u>http://www.systec-electronic.com</u>. The content of this website is updated periodically and provides to you downloads of the latest software releases and manual versions.

# Declaration of Electro Magnetic Conformity for PLCcore-9G20 (EMC law)

The PLCcore-9G20 has been designed to be used as vendor part for the integration into devices (further industrial processing) or as Development Board for laboratory development (hard- and software development).

After the integration into a device or when changes/extensions are made to this product, the conformity to EMC-law again must be assessed and certified. Only thereafter products may be launched onto the market.

The CE-conformity is only valid for the application area described in this document and only under compliance with the following commissioning instructions! The PLCcore-9G20 is ESD-sensitive and may only be unpacked, used and operated by trained personal at ESD-conform work stations.

The PLCcore-9G20 is a module for the application in automation technology. It features IEC 61131-3 programmability, uses standard CAN-bus and Ethernet network interfaces and a standardized network protocol. Consequently, development times are short and hardware costs are reasonable. PLC-functionality is created on-board through a CANopen network layer. Hence, it is not necessary for the user to create firmware.

# 2 Overview / Where to find what?

The PLCcore-9G20 is based on SYS TEC ECUcore-9G20 hardware and is extended by PLC-specific functionality (PLD software, PLC firmware). There are different hardware manuals for all hardware components such as the ECUcore-9G20 and the PLCcore-9G20 (the hardware of both modules is identical), development boards and reference circuitry. Software-sided, the PLCcore-9G20 is programmed with IEC 61131-3-conform *OpenPCS* programming environment. There are additional manuals for *OpenPCS* that describe the handling of programming tools and SYS TEC-specific extensions. Those are part of the software package "*OpenPCS*". Table 1 lists up all relevant manuals for the PLCcore-9G20.

| Information about                                                                                                                                                                        | In which manual?                                                                                                                                                           |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Basic information about the PLCcore-9G20<br>(configuration, administration, process image,<br>connection assignment, firmware update,<br>reference designs et cetera)                    | In this manual                                                                                                                                                             |

| Development of user-specific C/C++ applications<br>for the ECUcore-9G20 / PLCcore-9G20, VMware-<br>Image of the Linux development system                                                 | System Manual ECUcore-9G20<br>(Manual no.: L-1253)                                                                                                                         |

| Hardware description about the ECUcore-9G20 / PLCcore-9G20, reference designs et cetera                                                                                                  | Hardware Manual ECUcore-9G20<br>(Manual no.: L-1255)                                                                                                                       |

| Development Board for the ECUcore-9G20 /<br>PLCcore-9G20, reference designs et cetera                                                                                                    | Hardware Manual Development Board 9G20<br>(Manual no.: L-1256)                                                                                                             |

| Driver Development Kit (DDK) for the ECUcore-<br>9G20                                                                                                                                    | Software Manual Driver Development Kit (DDK)<br>for ECUcore-9G20<br>(Manual no.: L-1257)                                                                                   |

| Basics about the <i>OpenPCS</i> IEC 61131 programming system                                                                                                                             | Brief instructions for the programming system<br>(Entry " <i>OpenPCS Documentation</i> " in the<br><i>OpenPCS</i> program group of the start menu)<br>(Manual no.: L-1005) |

| Complete description of the <i>OpenPCS</i> IEC 61131 programming system, basics about the PLC programming according to IEC 61131-3                                                       | Online help about the <i>OpenPCS</i> programming system                                                                                                                    |

| Command overview and description of standard function blocks according to IEC 61131-3                                                                                                    | Online help about the <i>OpenPCS</i> programming system                                                                                                                    |

| <ul> <li>SYS TEC extension for IEC 61131-3:</li> <li>String functions</li> <li>UDP function blocks</li> <li>SIO function blocks</li> <li>FB for RTC, Counter, EEPROM, PWM/PTO</li> </ul> | User Manual "SYS TEC-specific extensions for<br>OpenPCS / IEC 61131-3"<br>(Manual no.: L-1054)                                                                             |

Table 1: Overview of relevant manuals for the PLCcore-9G20

L-1254e\_1

| CANopen extension for IEC 61131-3                       | User Manual <i>"CANopen extension for IEC 61131-3"</i>                                                                                                                                                   |

|---------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (Network variables, CANopen function blocks)            | (Manual no.: L-1008)                                                                                                                                                                                     |

| Textbook about PLC programming according to IEC 61131-3 | IEC 61131-3: Programming Industrial Automation<br>Systems<br>John/Tiegelkamp<br>Springer-Verlag<br>ISBN: 3-540-67752-6<br>(a short version is available as PDF on the<br><i>OpenPCS</i> installation CD) |

- Section 4 of this manual explains the commissioning of the PLCcore-9G20 based on the Development Kit for the PLCcore-9G20.

- Section 5 describes the connection assignment of the PLCcore-9G20.

- Section 6 explains details about the application of the PLCcore-9G20, e.g. the setup of the process image, the meaning of control elements and it provides basic information about programming the module. Moreover, information is given about the usage of CAN interfaces in connection with CANopen.

- Section 0 describes details about the configuration of the PLCcore-9G20, e.g. the configuration of Ethernet and CAN interfaces, the Linux Autostart procedure as well as choosing the firmware version. Furthermore, the administration of the PLCcore-9G20 is explained, e.g. the login to the system, the user administration and the execution of software updates.

- Section 8 defines the adaptation of in- and outputs as well as the process image and it covers the data exchange between a PLC program and a user-specific C/C++ application via shared process image.

| STSTEC Electronic Griph 2010 L-1234e I Page / | © SYS TEC electronic GmbH 2010 | L-1254e 1 | Page 7 |

|-----------------------------------------------|--------------------------------|-----------|--------|

|-----------------------------------------------|--------------------------------|-----------|--------|

# **3 Product Description**

The PLCcore-9G20 as another innovative product extends the SYS TEC electronic GmbH product range within the field of control applications. In the form of an insert-ready core module, it provides to the user a complete and compact PLC. Due to CAN and Ethernet interfaces, the PLCcore-9G20 is best suitable to perform decentralized control tasks.

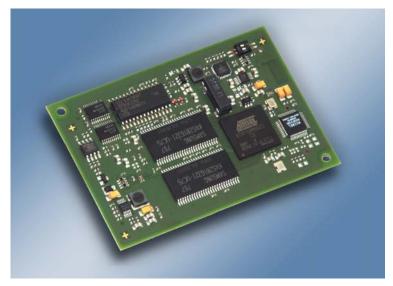

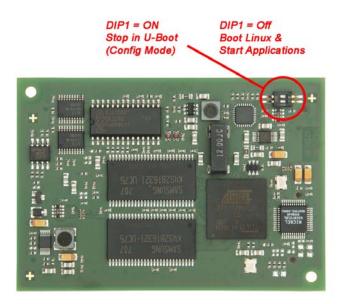

Figure 1: Top view of the PLCcore-9G20

These are some significant features of the PLCcore-9G20:

- High-performance CPU kernel (Atmel 32-Bit AT91SAM9G20, 400 MHz CPU Clock, 440 MIPS)

- 32 MByte SDRAM Memory, 16 MByte FLASH Memory (max: 64 MByte SDRAM Memory, 64 MByte FLASH Memory)

- 1x 10/100 Mbps Ethernet LAN interface (1x with on-board PHY)

- 1x CAN 2.0B interface, usable as CANopen Manager (CiA 302-conform)

- 5x asynchronous serial ports (UART)

- 19 digital inputs, 8 digital outputs (standard configuration, modifiable via DDK)

- 3 analog inputs

- 4 high-speed counter (Pulse/Dir or A/B)

- 4 PWM-/PTO output (Pulse/Dir)

- Externally usable SPI and I<sup>2</sup>C

- On-board peripherals: RTC, temperature sensor

- On-board software: Linux, PLC firmware, CANopen Master, HTTP and FTP server

- Programmable in IEC 61131-3 and in C/C++

- Function block libraries for communication (CANopen, Ethernet and UART)

- Function block libraries for hardware components (RTC, Counter, PWM/PTO)

- Support of typical PLC control elements (e.g. Run/Stop switch, Run-LED, Error-LED)

- Linux-based (other user programs may run in parallel)

- Easy, HTML-based configuration via WEB Browser

- Remote Login via Telnet

- Small dimension (78 x 54 mm)

There are different types of firmware available for the PLCcore-9G20. They differ regarding the protocol used for the communication between Programming PC and PLCcore-9G20:

| © SYS TEC electronic GmbH 2010 | L-1254e_1 | Page 8 |  |

|--------------------------------|-----------|--------|--|

|--------------------------------|-----------|--------|--|

| Order number: 3390024: | PLCcore-9G20/Z4 (CANopen)<br>communication with Programming PC via CANopen Protocol<br>(Interface CAN0) |

|------------------------|---------------------------------------------------------------------------------------------------------|

| Order number: 3390025: | PLCcore-9G20/Z5 (Ethernet)<br>communication with Programming PC via UDP Protocol<br>(Interface ETH0)    |

Making PLC available as an insert-ready core module with small dimensions reduces effort and costs significantly for the development of user-specific controls. The PLCcore-9G20 is also very well suitable as intelligent network node for decentralized processing of process signals (CANopen and UDP). Additionally, it can be used as basic component for special assemblies or as PLC in hard-to-access areas.

The on-board firmware of the PLCcore-9G20 contains the entire PLC runtime environment including CANopen connection with CANopen master functionality. Thus, the module is able to perform control tasks such as linking in- and outputs or converting rule algorithms. Data and occurrences can be exchanged with other nodes (e.g. superior main controller, I/O slaves and so forth) via CANopen network, Ethernet (UDP protocol) and serial interfaces (UART). Moreover, the number of in- and outputs either is locally extendable or decentralized via CANopen devices. For this purpose, the CANopen-Chip is suitable. It has also been designed as insert-ready core module for the appliance in user-specific applications.

The PLCcore-9G20 provides 19 digital inputs (DI0...DI23, 3.3V level), 8 digital outputs (DO0...DO21, 3.3V level), 4 high-speed counter input and 4 PWM/PTO output. This default I/O configuration can be adapted for specific application requirements by using the Driver Development Kit (SO-1106).Saving the PLC program in the on-board Flash-Disk of the module allows an automatic restart in case of power breakdown.

Programming the PLCcore-9G20 takes place according to IEC 61131-3 using the *OpenPCS* programming system of the company infoteam Software GmbH (<u>http://www.infoteam.de</u>). This programming system has been extended and adjusted for the PLCcore-9G20 by the company SYS TEC electronic GmbH. Hence, it is possible to program the PLCcore-9G20 graphically in KOP/FUB, AS and CFC or textually in AWL or ST. Downloading the PLC program onto the module takes place via Ethernet or CANopen – depending on the firmware that is used. Addressing in- and outputs and creating a process image follows the SYS TEC scheme for compact control units. Like all other SYS TEC controls, the PLCcore-9G20 supports backward documentation of the PLC program as well as the debug functionality including watching and setting variables, single cycles, breakpoints and single steps.

The PLCcore-9G20 is based on Embedded Linux as operating system. This allows for an execution of other user-specific programs while PLC firmware is running. If necessary, those other user-specific programs may interchange data with the PLC program via the process image. More information about this is provided in section 8.

The Embedded Linux applied to the PLCcore-9G20 is licensed under GNU General Public License, version 2. Appendix C contains the license text. All sources of LinuxBSP are included in the software package **SO-1105** ("VMware-Image of the Linux development system for the ECUcore-9G20"). If you require the LinuxBSP sources independently from the VMware-Image of the Linux development system, please contact our support:

support@systec-electronic.com

The PLC system and the PLC- and C/C++ programs developed by the user are **not** subject to GNU General Public License!

| © SYS TEC electronic GmbH 2010 | L-1254e 1 | Page 9 |  |

|--------------------------------|-----------|--------|--|

|                                |           |        |  |

# 4 Development Kit PLCcore-9G20

### 4.1 Overview

The Development Kit PLCcore-9G20 is a high-capacity, complete package at a particularly favorable price. Based on a compact PLC, it enables the user to perform decentralized, network-compatible automation projects. Moreover, it facilitates the user to get to know the advantages of graphical and textual PLC programming according to IEC 61131-3 – compared to conventional programming languages.

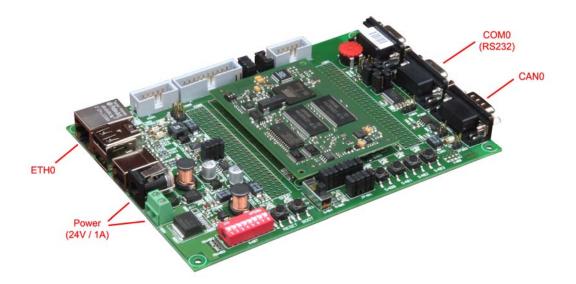

Figure 2: Development Kit PLCcore-9G20

The Development Kit PLCcore-9G20 ensures quick and problem-free commissioning of the PLCcore-9G20. Therefore, it combines all hard- and software components that are necessary to create own applications: the core module PLCcore-9G20, the corresponding Development Board containing I/O periphery and numerous interfaces, the *OpenPCS* IEC 61131 programming system as well as further accessory. Thus, the Development Kit forms the ideal platform for developing user-specific applications based on the PLCcore-9G20. It allows for a cost-efficient introduction into the world of decentralized automation technology. All components included in the Kit enable in- and output extensions of the PLCcore-9G20 through CANopen-I/O-assemblies. Thus, the Development Kit may also be used for projects that require PLC with network connection.

The Development Kit PLCcore-9G20 contains the following hardware components:

- PLCcore-9G20

- Development Board for the PLCcore-9G20

- 24V DC Power adapter

- Ethernet cable

- RS232 cable

- CD with programming software, examples, documentation and other tools

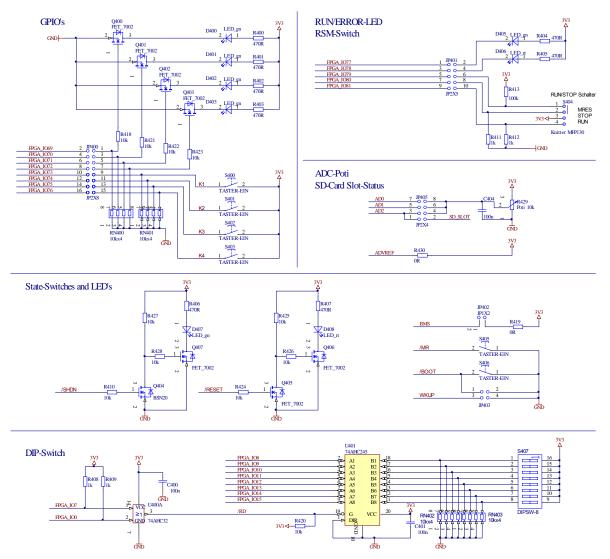

The Development Board included in the Kit facilitates quick commissioning of the PLCcore-9G20 and simplifies the design of prototypes for user-specific applications based on this module. Among other equipment, the Development Board comprises different power supply possibilities, Ethernet interface, CAN interface, 4 push buttons and 4 LED as control elements for digital in- and outputs and it comprises a potentiometer for the analog input. Signals that are available from plug connectors of the PLCcore-9G20 are linked to pin header connectors and enable easy connection of own peripheral

| © SYS TEC electronic GmbH 2010 | L-1254e_1 | Page 10 |  |

|--------------------------------|-----------|---------|--|

|--------------------------------|-----------|---------|--|

circuitry. Hence, the Development Board forms an ideal experimentation and testing platform for the PLCcore-9G20.

The *OpenPCS* IEC 61131 programming system included in the Kit serves as software development platform and as debug environment for the PLCcore-9G20. Thus, the module can either be programmed graphically in KOP/FUB, AS and CFC or textually in AWL or ST. Downloading the PLC program onto the module takes place via Ethernet or CANopen – depending on the firmware that is used. High-capacity debug functionality such as watching and setting variables, single cycles, breakpoints and single steps simplify the development and commissioning of user software for this module.

### 4.2 Electric commissioning of the Development Kit PLCcore-9G20

A 24V DC power adapter necessary for running the Development Kit PLCcore-9G20 and Ethernet and RS232 cables are already included in the Kit delivery. For commissioning the Kit, it is essential to use at least the power supply connections (X700/X701), COM0 (X400 on top) and ETH0 (X500). Furthermore, connection CAN0 (X400 below) is recommended. Table 2 provides an overview over the connections of the Development Kit PLCcore-9G20.

| Connection      | Labeling on the<br>Development<br>Board | Remark                                                                                                                                                                                                                   |

|-----------------|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power supply    | X600 oder X601                          | The 24V DC power adapter included in the delivery is intended for direct connection to X700.                                                                                                                             |

| ETH0 (Ethernet) | X304                                    | This interface serves as communication interface<br>with the Programming PC and is necessary for the<br>program download (PLCcore-9G20/Z5, order<br>number 3390025), besides can be used freely for<br>the user program. |

| COM0 (RS232)    | X301                                    | This interface is used for the configuration of the<br>unit (e.g. setting the IP-address) and can be used<br>freely for general operation of the user program.                                                           |

| COM1 (RS232)    | X300                                    | Interface can be used freely for the user program.                                                                                                                                                                       |

| COM2 (RS232)    | X302n                                   | Interface can be used freely for the user program.                                                                                                                                                                       |

| CAN0 (CAN)      | X303                                    | This interface serves as communication interface<br>with the Programming PC and is necessary for the<br>program download (PLCcore-9G20/Z4, order<br>number 3390024), besides can be used freely for<br>the user program. |

Table 2: Connections of the Development Kit PLCcore-9G20

Figure 3 shows the positioning of the most important connections of the Development Board for the PLCcore-9G20. Instead of using the 24V DC power adapter included in the Kit, the power supply may optionally take place via X601 with an external source of 24V/1A.

| © SYS TEC electronic GmbH 2010 | L-1254e 1 | Page 11 |

|--------------------------------|-----------|---------|

|                                |           |         |

Figure 3: Positioning of most important connections on the Development Board for the PLCcore-9G20

# Advice: Upon commissioning, cables for Ethernet (ETH0, X304) and RS232 (COM0, X301) must be connected prior to activating the power supply (X600 / X601).

## 4.3 Control elements of the Development Kit PLCcore-9G20

The Development Kit PLCcore-9G20 allows for easy commissioning of the PLCcore-9G20. It has available various control elements to configure the module and to simulate in- and outputs for the usage of the PLCcore-9G20 as PLC kernel. In Table 3 control elements of the Development Board are listed and their meaning is described.

| Control element | Name | Meaning                                                                  |                 |         |

|-----------------|------|--------------------------------------------------------------------------|-----------------|---------|

| Pushbutton 0    | S400 | Digital Input DI0                                                        | (Process Image: | %IX0.0) |

| Pushbutton 1    | S401 | Digital Input DI1                                                        | (Process Image: | %IX0.1) |

| Pushbutton 2    | S402 | Digital Input DI2                                                        | (Process Image: | %IX0.2) |

| Pushbutton 3    | S403 | Digital Input DI3                                                        | (Process Image: | %IX0.3) |

| LED 0           | D400 | Digital Output DO0                                                       | (Process Image: | %QX0.0) |

| LED 1           | D401 | Digital Output DO1                                                       | (Process Image: | %QX0.1) |

| LED 2           | D402 | Digital Output DO2                                                       | (Process Image: | %QX0.2) |

| LED 3           | D403 | Digital Output DO3                                                       | (Process Image: | %QX0.3) |

| Poti (ADC)      | R429 | Analog Input AI0                                                         | (Process Image: | %IW8.0) |

| Run/Stop Switch | S404 | Run / Stop to operate the PLC program, Reset control (see section 6.7.1) |                 |         |

Table 3: Control elements of the Development Board for the PLCcore-9G20

| Run-LED    | D405 | Display of activity state of the PLC (see section 6.7.2)          |

|------------|------|-------------------------------------------------------------------|

| Error-LED  | D406 | Display of error state of the PLC (see section 6.7.3)             |

|            |      |                                                                   |

| DIP-Switch | S407 | Configuration of bitrate and master mode CAN0 (see section 7.4.2) |

Table 8 in section 6.4.1 provides a complete listing of the process image.

#### 4.4 Optional accessory

#### 4.4.1 USB-RS232 Adapter Cable

The SYS TEC USB-RS232 Adapter Cable (order number 3234000) provides a RS232 interface via an USB-Port of the PC. Together with a terminal program, it enables the configuration of the PLCcore-9G20 from PCs, e.g. laptop computers which do not have RS232 interfaces any more (see section 6.1).

Figure 4: SYS TEC USB-RS232 Adapter Cable

#### 4.4.2 Driver Development Kit (DDK)

The ECUcore-9G20 Driver Development Kit (order number SO-1106) allows the user to independently adjust the I/O level to his own baseboard. Section 8.2 provides information about the Driver Development Kit.

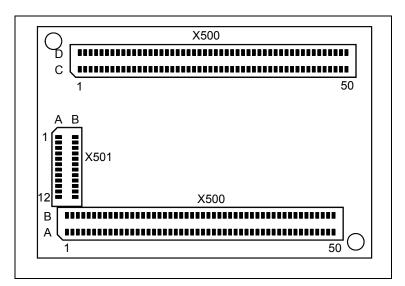

# 5 Pinout of the PLCcore-9G20

Connections of the PLCcore-9G20 are directed to the outside via two female headers that are doublerow and mounted on the bottom of the module (X500, see Figure 5). Appropriate pin header connectors as correspondent to the PLCcore-9G20 are available from company "W + P":

W+P name:SMT Pin Headers, 1.27mm Pitch, Vertical, Double Row - 1.0mm BodyW+P order number:7072-100-10-00-10-PPST (deliverable in other sizes)

Figure 5: Pinout of the PLCcore-9G20 - top view

Figure 5 exemplifies the positioning of female headers (X500) on the PLCcore-9G20. The complete connection assignment of this module is listed up in Table 4. The additional female header X501 shown in Figure 5 is reserved for a JTAG interface. It is only equipped on special development boards. For the usage of the PLCcore-9G20 as PLC kernel it is without any importance. A detailed description of all module connectors is located in the Hardware Manual ECUcore-9G20 (Manual no.: L-1255). Appendix B includes reference designs for using the PLCcore-9G20 in customer-specific applications.

| Signal | Pin | Pin | Signal | Signal   | Pin | Pin | Signal       |

|--------|-----|-----|--------|----------|-----|-----|--------------|

| GND    | A01 | B01 | GND    | GND      | C01 | D01 | +2V5_EPHY    |

| /BOOT  | A02 | B02 | /MR    | ETH0_TX- | C02 | D02 | GND          |

| WKUP   | A03 | B03 | /RESET | ETH0_TX+ | C03 | D03 | ETH_SPEED    |

| SHDN   | A04 | B04 | /PFI   | ETH0_RX+ | C04 | D04 | ETH_LINK/ACT |

| BMS    | A05 | B05 | WDI    | ETH0_RX- | C05 | D05 | GND          |

| GND    | A06 | B06 | PS_IO  | GND      | C06 | D06 | AD0          |

| DRXD   | A07 | B07 | GND    | ADTRG    | C07 | D07 | AD1          |

| DTXD   | A08 | B08 | RTS0   | ADVREF   | C08 | D08 | AD2          |

| DSR0   | A09 | B09 | CTS0   | GND      | C09 | D09 | GND          |

| DTR0   | A10 | B10 | RTS1   | SD_MCDA0 | C10 | D10 | SD_MCDB0     |

| DCD0   | A11 | B11 | CTS1   | SD_MCDA1 | C11 | D11 | SD_MCDB1     |

| GND    | A12 | B12 | GND    | SD_MCDA2 | C12 | D12 | SD_MCDB2     |

| TXD0   | A13 | B13 | TXD1   | SD_MCDA3 | C13 | D13 | SD_MCDB3     |

| RXD0   | A14 | B14 | RXD1   | SD_MCCK  | C14 | D14 | SD_MCCDA     |

| TXD2   | A15 | B15 | TXD3   | GND      | C15 | D15 | SD_MCCDB     |

| Table 4: Connections of the PLCcore-9G20, | completely sorted  | l by connection pin |

|-------------------------------------------|--------------------|---------------------|

|                                           | completely, soliet |                     |

| 4e_1 Page 14 |              |

|--------------|--------------|

| ,            | 4e_1 Page 14 |

| Signal    | Pin | Pin | Signal    |   | Signal    | Pin | Pin | Signal    |

|-----------|-----|-----|-----------|---|-----------|-----|-----|-----------|

| RXD2      | A16 | B16 | RXD3      |   | SCK0      | C16 | D16 | GND       |

| GND       | A17 | B17 | TXD5      | Γ | SCK1      | C17 | D17 | TIOA1     |

| USB_HDPA  | A18 | B18 | RXD5      | Γ | SCK2      | C18 | D18 | TIOB1     |

| USB_HDMA  | A19 | B19 | GND       | Γ | PCK1      | C19 | D19 | TIOA2     |

| USB_HDPB  | A20 | B20 | USB_DDP   |   | RK0       | C20 | D20 | TIOB2     |

| USB_HDMB  | A21 | B21 | USB_DDM   | Γ | TK0       | C21 | D21 | TD0       |

| GND       | A22 | B22 | GND       |   | RF0       | C22 | D22 | RD0       |

| I2C_DATA  | A23 | B23 | CAN_TXD   | Γ | TF0       | C23 | D23 | GND       |

| I2C_CLK   | A24 | B24 | CAN_RXD   |   | GND       | C24 | D24 | FPGA_IO0  |

| GND       | A25 | B25 | CAN_VCC   |   | FPGA_IO1  | C25 | D25 | FPGA_IO2  |

| FPGA_IO44 | A26 | B26 | GND       | Γ | FPGA_IO3  | C26 | D26 | FPGA_IO4  |

| FPGA_IO46 | A27 | B27 | FPGA_IO45 |   | FPGA_IO5  | C27 | D27 | FPGA_IO6  |

| FPGA_IO48 | A28 | B28 | FPGA_IO47 |   | FPGA_IO7  | C28 | D28 | GND       |

| FPGA_IO50 | A29 | B29 | FPGA_IO49 |   | GND       | C29 | D29 | FPGA_IO8  |

| FPGA_IO52 | A30 | B30 | FPGA_IO51 |   | FPGA_IO9  | C30 | D30 | FPGA_IO10 |

| GND       | A31 | B31 | FPGA_IO53 |   | FPGA_IO11 | C31 | D31 | FPGA_IO12 |

| FPGA_IO54 | A32 | B32 | GND       | Γ | FPGA_IO13 | C32 | D32 | FPGA_IO14 |

| FPGA_IO56 | A33 | B33 | FPGA_IO55 |   | FPGA_IO15 | C33 | D33 | GND       |

| FPGA_IO58 | A34 | B34 | FPGA_IO57 | Γ | FPGA_IO17 | C34 | D34 | FPGA_IO16 |

| FPGA_IO60 | A35 | B35 | FPGA_IO59 |   | GND       | C35 | D35 | FPGA_IO18 |

| FPGA_IO62 | A36 | B36 | FPGA_IO61 | Γ | FPGA_IO19 | C36 | D36 | FPGA_IO20 |

| GND       | A37 | B37 | FPGA_IO63 |   | FPGA_IO21 | C37 | D37 | FPGA_IO22 |

| FPGA_IO64 | A38 | B38 | GND       |   | FPGA_IO23 | C38 | D38 | FPGA_IO24 |

| FPGA_IO66 | A39 | B39 | FPGA_IO65 | Γ | FPGA_IO25 | C39 | D39 | GND       |

| FPGA_IO68 | A40 | B40 | FPGA_IO67 |   | FPGA_IO27 | C40 | D40 | FPGA_IO26 |

| FPGA_IO70 | A41 | B41 | FPGA_IO69 | Γ | GND       | C41 | D41 | FPGA_IO28 |

| FPGA_I072 | A42 | B42 | FPGA_IO71 | Γ | FPGA_IO29 | C42 | D42 | FPGA_IO30 |

| GND       | A43 | B43 | FPGA_IO73 |   | FPGA_IO31 | C43 | D43 | FPGA_IO32 |

| FPGA_IO74 | A44 | B44 | GND       | Γ | FPGA_IO33 | C44 | D44 | FPGA_IO34 |

| FPGA_IO76 | A45 | B45 | FPGA_IO75 | ſ | FPGA_IO35 | C45 | D45 | GND       |

| FPGA_IO78 | A46 | B46 | FPGA_IO77 | ſ | FPGA_IO37 | C46 | D46 | FPGA_IO36 |

| FPGA_IO80 | A47 | B47 | FPGA_IO79 | ſ | GND       | C47 | D47 | FPGA_IO38 |

| VBAT      | A48 | B48 | FPGA_IO81 | ſ | FPGA_IO39 | C48 | D48 | FPGA_IO40 |

| GND       | A49 | B49 | GND       | ſ | FPGA_IO41 | C49 | D49 | FPGA_IO42 |

| +3V3      | A50 | B50 | +3V3      |   | FPGA_IO43 | C50 | D50 | GND       |

Table 5 is a subset of Table 4 and only includes all in- and outputs of the PLCcore-9G20 sorted by their function.

| Connector | I/O-Pin (FPGA) | PLC Function 1 | PLC Function 2<br>A=alternative, S=simultaneous |

|-----------|----------------|----------------|-------------------------------------------------|

|           |                |                |                                                 |

| B43       | 1073           | DI0 [Switch0]  | S: CNTR0 (IN/A)                                 |

| A44       | 1074           | DI1 [Switch1]  | S: CNTR0 ('DIR/B)                               |

| B45       | 1075           | DI2 [Switch2]  | S: CNTR1 (IN/A)                                 |

| A45       | 1076           | DI3 [Switch3]  | S: CNTR1 ('DIR/B)                               |

| B39       | IO65           | DI4            |                                                 |

| A39       | IO66           | DI5            |                                                 |

| B40       | 1067           | DI6            |                                                 |

| A40       | IO68           | DI7            |                                                 |

|           |                |                |                                                 |

| A29 | IO50 | DI8          | S: CNTR2 (IN/A)  |

|-----|------|--------------|------------------|

| B30 | IO51 | DI9          | S: CNTR2 (DIR/B) |

| A30 | IO52 | DI10         | S: CNTR3 (IN/A)  |

| B31 | IO53 | DI11         | S: CNTR3 (DIR/B) |

| A32 | IO54 | DI12         |                  |

| B33 | IO55 | DI13         |                  |

| A33 | IO56 | DI14         |                  |

| B34 | IO57 | DI15         |                  |

| A34 | 1058 | DI16         |                  |

| B35 | 1059 | DI17         |                  |

| A35 | 1060 | DI18         |                  |

|     |      |              |                  |

| B41 | IO69 | DO0 [LED0]   | A: PWM0 (OUT)    |

| A41 | IO70 | DO1 [LED1]   | A: PWM1 (OUT)    |

| B42 | IO71 | DO2 [LED2]   | A: PWM2 (OUT)    |

| A42 | IO72 | DO3 [LED3]   | A: PWM3 (OUT)    |

| B36 | IO61 | DO4          |                  |

| A36 | IO62 | DO5          |                  |

| B37 | IO63 | DO6          |                  |

| A38 | IO64 | DO7          |                  |

| A46 | IO78 | /Error-LED   |                  |

| B46 | 1077 | /Run-LED     |                  |

| B47 | 1079 | R/S/M-Switch |                  |

| A47 | 1080 | R/S/M-Switch |                  |

| B48 | IO81 | R/S/M-Switch |                  |

|     |      |              |                  |

|     |      |              |                  |

Table 6 defines the coding of the Run/Stop switch. Functionality of the Run/Stop switch for PLC firmware is explained in section 6.7.1. If no Run/Stop switch is intended for the usage of the PLCcore-9G20 on an application-specific baseboard, the coding for *"Run"* must be hard-wired at the module connections (also see reference design in Appendix B).

Table 6: Coding of the Run/Stop switch

| Modus | Pin B47<br>(IO79) | Pin A47<br>(IO80) | Pin B48<br>(IO81) |

|-------|-------------------|-------------------|-------------------|

| Run   | 1                 | 0                 | 1                 |

| Stop  | 1                 | 1                 | 0                 |

| MRes  | 0                 | 0                 | 0                 |

# 6 PLC Functionality of the PLCcore-9G20

### 6.1 Overview

The PLCcore-9G20 realizes a complete Linux-based compact PLC as an insert-ready core ("Core"). There, the PLCcore-9G20 is based on the hardware ECUcore-9G20 and extends it by PLC-specific functionality (FPGA software, PLC firmware). Both modules, the ECUcore-9G20 and the PLCcore-9G20, use the same Embedded Linux as operating system. Consequently, the configuration and the C/C++ programming of the PLCcore-9G20 are almost identical with the ECUcore-9G20.

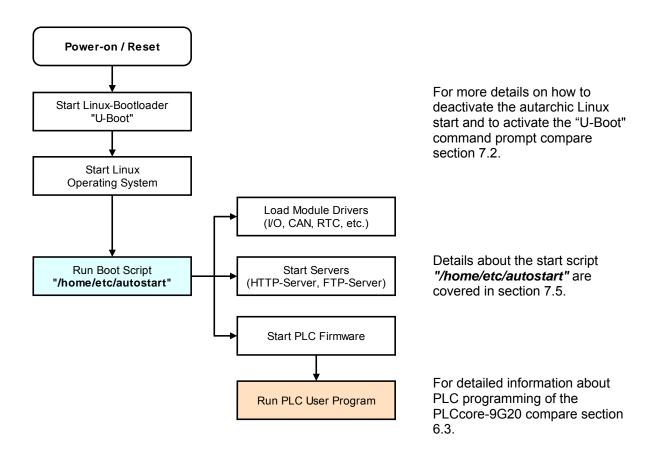

# 6.2 System start of the PLCcore-9G20

By default, the PLCcore-9G20 loads all necessary firmware components upon Power-on or Reset and starts running the PLC program afterwards. Hence, the PLCcore-9G20 is suitable for the usage in autarchic control systems. In case of power breakdown, such systems resume the execution of the PLC program independently and without user intervention. Figure 6 shows the system start in detail:

Figure 6: System start of the PLCcore-9G20

## 6.3 Programming the PLCcore-9G20

The PLCcore-9G20 is programmed with IEC 61131-3-conform *OpenPCS* programming environment. There exist additional manuals about *OpenPCS* that describe the handling of this programming tool. Those are part of the software package "*OpenPCS*". All manuals relevant for the PLCcore-9G20 are listed in Table 1.

PLCcore-9G20 firmware is based on standard firmware for SYS TEC's compact control units. Consequently, it shows identical properties like other SYS TEC control systems. This affects especially the process image setup (see section 6.4) as well as the functionality of control elements (Hex-Encoding switch, DIP-Switch, Run/Stop switch, Run-LED, Error-LED).

Depending on the firmware version used, PLCcore-9G20 firmware provides numerous function blocks to the user to access communication interfaces. Table 7 specifies the availability of FB communication classes (SIO, CAN, UDP) for different PLCcore-9G20 firmware versions. Section 7.6 describes the selection of the appropriate firmware version.

| Type of<br>Interface | PLCcore-9G20/Z3<br>Art. no: 3390023 | PLCcore-9G20/Z4<br>Art. no: 3390024 | PLCcore-9G20/Z5<br>Art. no: 3390025 | Remark                              |

|----------------------|-------------------------------------|-------------------------------------|-------------------------------------|-------------------------------------|

| CAN                  | -                                   | х                                   | Х                                   | FB description see<br>manual L-1008 |

| UDP                  | -                                   | Х                                   | Х                                   | FB description see<br>manual L-1054 |

| SIO                  | х                                   | х                                   | Х                                   | FB description see<br>manual L-1054 |

#### Table 7: Support of FB communication classes for different types of the PLCcore

Table 22 in Appendix A contains a complete listing of firmware functions and function blocks that are supported by the PLCcore-9G20.

Detailed information about using the CAN interfaces in connection with CANopen is provided in section 6.9.

# 6.4 Process image of the PLCcore-9G20

#### 6.4.1 Local In- and Outputs

Compared to other SYS TEC compact control systems, the PLCcore-9G20 obtains a process image with identical addresses. All in- and outputs listed in Table 8 are supported by the PLCcore-9G20.

Table 8: Assignment of in- and outputs to the process image of the PLCcore-9G20

| I/O of the PLCcore-9G20                                               | Address and Data ty                 | pe in the Process Image                                                                  |

|-----------------------------------------------------------------------|-------------------------------------|------------------------------------------------------------------------------------------|

| DI0 DI7                                                               | <b>%IB0.0</b><br>%IX0.0 … %IX0.7    | as Byte with DI0 … DI7<br>as single Bit for each input                                   |

| DI8 DI15                                                              | <b>%IB1.0</b><br>%IX1.0 … %IX1.7    | as Byte with DI8 … DI15<br>as single Bit for each input                                  |

| DI16 DI23<br>(DI19 DI23 as user specific<br>extension only)           | <b>%IB2.0</b><br>%IX2.0 %IX2.7      | as Byte with DI16 … DI23<br>as single Bit for each input                                 |

| DI24 DI31<br>(as user specific extension only)                        | <b>%IB3.0</b><br>%IX3.0 … %IX3.7    | as Byte with DI24 … DI31<br>as single Bit for each input                                 |

| DI32 DI39<br>(as user specific extension only)                        | <b>%IB4.0</b><br>%IX4.0 … %IX4.7    | as Byte with DI32 … DI139<br>as single Bit for each input                                |

| DI40 DI47<br>(as user specific extension only)                        | <b>%IB5.0</b><br>%IX5.0 … %IX5.7    | as Byte with DI40 … DI47<br>as single Bit for each input                                 |

| Al0<br>(external ADC of the Development<br>Board), see <sup>(1)</sup> | %IW8.0                              | 15Bit + sign (0 … +32767)                                                                |

| C0                                                                    | %ID40.0<br>counter input: DI0, dire | 31Bit + sign (-2 <sup>31</sup> - 2 <sup>31</sup> -1)<br>ection: DI1, see section 6.6.1   |

| C1                                                                    | %ID44.0<br>counter input: DI2, dire | 31Bit + sign (-2 <sup>31</sup> - 2 <sup>31</sup> -1)<br>ection: DI3, see section 6.6.1   |

| C2                                                                    | %ID48.0<br>counter input: DI8 dire  | 31Bit + sign (-2 <sup>31</sup> - 2 <sup>31</sup> -1)<br>ction: DI9, see section 6.6.1    |

| C3                                                                    | %ID52.0<br>counter input: DI10, di  | 31Bit + sign (-2 <sup>31</sup> - 2 <sup>31</sup> -1)<br>rection: DI11, see section 6.6.1 |

| On-board Temperature Sensor, see <sup>(1)</sup>                       | %ID72.0                             | 31Bit + sign as 1/10000 °C                                                               |

| DO0 DO7                                                               | <b>%QB0.0</b><br>%QX0.0 %QX0.7      | as Byte with DO0 … DO7<br>as single Bit for each output                                  |

| DO8 DO15<br>(as user specific extension only)                         | <b>%QB1.0</b><br>%QX1.0 %QX1.7      | as Byte with DO8 … DO15<br>as single Bit for each output                                 |

| DO16 DO23<br>(as user specific extension only)                        | <b>%QB2.0</b><br>%QX2.0 %QX2.7      | as Byte with DO16 … DO23<br>as single Bit for each output                                |

| DO24 DO31<br>(as user specific extension only)                        | <b>%QB3.0</b><br>%QX3.0 %QX3.7      | as Byte with DO24 … DO31<br>as single Bit for each output                                |

| DO32 … DO39<br>(as user specific extension only)                      | <b>%QB4.0</b><br>%QX4.0 %QX4.7      | as Byte with DO32 … DO39<br>as single Bit for each output                                |

| DO40 DO47<br>(as user specific extension only)                        | <b>%QB5.0</b><br>%QX5.0 %QX5.7      | as Byte with DO40 … DO47<br>as single Bit for each output                                |

© SYS TEC electronic GmbH 2010

L-1254e\_1

| P0 | <b>%QX0.0</b> (default value for inactive generator)<br>Impulse output: DO0, see section 6.6.2 |

|----|------------------------------------------------------------------------------------------------|

| P1 | <b>%QX0.1</b> (default value for inactive generator)<br>Impulse output: DO1, see section 6.6.2 |

| P2 | <b>%QX0.2</b> (default value for inactive generator)<br>Impulse output: DO2, see section 6.6.2 |

| Р3 | <b>%QX0.3</b> (default value for inactive generator)<br>Impulse output: DO3, see section 6.6.2 |

(1) This marked components are only available in the process image, if the **Option "Enable extended I/Os"** is activated within the PLC configuration (see section 7.4.1). Alternatively, entry "EnableExtlo=" can directly be set within section "[ProcImg]" of the configuration file "/home/plc/plccore-9g20.cfg" (see section 7.4.3). The appropriate configuration setting is evaluated upon start of the PLC firmware.

In- and outputs of thePLCcore-9G20 are not negated in the process image. Hence, the H-level at one input leads to value "1" at the corresponding address in the process image. Contrariwise, value "1" in the process image leads to an H-level at the appropriate output.

#### 6.4.2 In- and outputs of user-specific baseboards

The connection lines leading towards the outside provides to the user most effective degrees of freedom for designing the in-/output circuit of the PLCcore-9G20. Therewith, all in- and outputs of the PLCcore-9G20 can be flexibly adjusted to respective requirements. This implicates that the process image of PLCcore-9G20 is significantly conditioned by the particular, user-specific in-/output circuit. Including the software for in-/output components into the process image requires the "*Driver Development Kit for ECUcore-9G20*" (order number SO-1106).

#### 6.5 Communication interfaces

#### 6.5.1 Serial interfaces

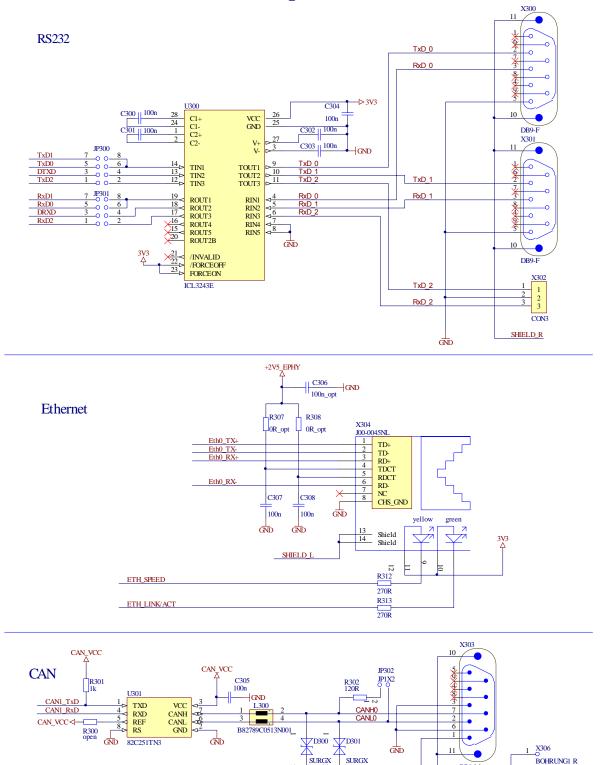

The PLCcore-9G20 features 5 serial interfaces (COM0 ... COM4) that function as RS-232. Details about hardware activation are included in the *"Hardware Manual Development Board ECUcore-9G20"* (Manual no.: L-1256).

**COM0:** Interface COM0 primarily serves as service interface to administer the PLCcore-9G20. By default, in boot script "/etc/inittab" it is assigned to the Linux process "getty" and is used as Linux console to administer the PLCcore-9G20. Even though interface COM0 may be used from a PLC program via function blocks of type "SIO\_Xxx" (see manual "SYS TEC-specific Extensions for OpenPCS / IEC 61131-3", Manual no.: L-1054), only signs should be output in this regard. The module tries to interpret and to execute signs that it receives as Linux commands.

To freely use an interface from a PLC program, boot script "/etc/inittab" must be adjusted appropriately which is only possible by modifying the Linux image. This requires software package SO-1105 ("VMware-Image of the Linux Development System for the ECUcore-9G20").

**COM1..4:** Interfaces COM1 ... COM4 are disposable and support data exchange between the PLCcore-9G20 and other field devices kept under control of the PLC program.

| © SYS TEC electronic GmbH 2010 | L-1254e_1 | Page 20 |  |

|--------------------------------|-----------|---------|--|

|--------------------------------|-----------|---------|--|

Interfaces COM1 ... COM4 may be used from a PLC program via function blocks of type "SIO\_Xxx" (see manual "SYS TEC-specific Extensions for OpenPCS / IEC 61131-3", Manual no.: L-1054).

#### 6.5.2 CAN interfaces

The PLCcore-9G20 features 1 CAN interface (CAN0). Details about the hardware activation are included in the *"Hardware Manual Development Board ECUcore-9G20"* (Manual no.: L-1256).

The CAN interface allow for data exchange with other devices via network variables and they are accessible from a PLC program via function blocks of type "CAN\_Xxx" (see section 6.9 and "User Manual CANopen Extension for IEC 61131-3", Manual no.: L-1008).

Section 6.9 provides detailed information about the usage of the CAN interface in connection with CANopen.

#### 6.5.3 Ethernet interfaces

The PLCcore-9G20 features 1 Ethernet interface (ETH0). Details about the hardware activation are included in the "Hardware Manual Development Board ECUcore-9G20" (Manual no.: L-1256).

The Ethernet interface serves as service interface to administer the PLCcore-9G20 and it enables data exchange with other devices. The interface is accessible from a PLC program via function blocks of type "LAN\_Xxx" (see manual "SYS TEC-specific Extensions for OpenPCS / IEC 61131-3", Manual no.: L-1054).

The exemplary PLC program "*UdpRemoteCtrl*" illustrates the usage of function blocks of type "*LAN\_Xxx*" within a PLC program.

#### 6.6 Specific peripheral interfaces

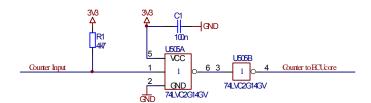

#### 6.6.1 Counter inputs

The PLCcore-9G20 features 4 fast counter inputs (C0 ... C3). Prior to its usage, all counter inputs must be parameterized via function block "*CNT\_FUD*" (see manual "SYS *TEC-specific Extensions for OpenPCS / IEC 61131 3*", Manual no.: L 1054). Afterwards, in a PLC program the current counter value is accessible via process image (see Table 8 in section 6.4.1) or via function block "*CNT\_FUD*". Table 9 lists the allocation between counter channels and inputs.

| Counter channel | Counter in | put    | Optional input | direction | Counter value in process image |

|-----------------|------------|--------|----------------|-----------|--------------------------------|

| C0              | C0 (DI0)   | %IX0.0 | DI1            | %IX0.1    | %ID40.0                        |

| C1              | C1 (DI2)   | %IX0.2 | DI3            | %IX0.3    | %ID44.0                        |

| C2              | C2 (DI8)   | %IX1.0 | DI9            | %IX1.1    | %ID48.0                        |

| C3              | C2 (DI10)  | %IX1.2 | DI11           | %IX1.3    | %ID52.0                        |

Table 9: Allocation between counter channels and inputs

| © SYS TEC electronic GmbH 2010 | L-1254e_1 | Page 21 |  |

|--------------------------------|-----------|---------|--|

|--------------------------------|-----------|---------|--|

To ensure the minimum slew rate for the counter inputs, required by FPGA, it is necessary to use the interface connection as shown in Figure 35 in Appendix B. A too small slew rate may lead to wrong counter values.

#### 6.6.2 Pulse outputs

To release PWM and PTO signal sequences, the PLCcore-9G20 features 4 pulse outputs (P0 ... P3). Prior to its usage, all pulse outputs must be parameterized using function block "*PTO\_PWM*" (see manual "SYS TEC-specific Extensions for OpenPCS / IEC 61131 3", Manual no.: L 1054). After the impulse generator is started, it takes over the control of respective outputs. After the impulse generator is deactivated, the respective output adopts the corresponding value that is filed in the process image for this output (see Table 8 in section 6.4.1). Table 10 lists the allocations between impulse channels and outputs.

| Impulse channel | Impulse output  |  |

|-----------------|-----------------|--|

| P0              | P0 (DO0) %QX0.0 |  |

| P1              | P1 (DO1) %QX0.1 |  |

| P2              | P0 (DO2) %QX0.2 |  |

| P3              | P1 (DO3) %QX0.3 |  |

Table 10: Allocation between impulse channels and outputs

### 6.7 Control and display elements

#### 6.7.1 Run/Stop switch

Module connections "IO79", "IO80" and "IO81" (see Table 5 and see reference design in Appendix B) are designed to connect a Run/Stop switch. Using this Run/Stop switch makes it possible to start and interrupt the execution of the PLC program. Together with start and stop pushbuttons of the *OpenPCS* programming environment, the Run/Stop switch represents a "logical" AND-relation. This means that the PLC program will not start the execution until the local Run/Stop switch is positioned to "Run" **AND** additionally the start command (cold, warm or hot start) is given by the *OpenPCS* user interface. The order hereby is not relevant. A run command given by *OpenPCS* while at the same time the Run/Stop switch is positioned to "Stop" is visible through quick flashing of the Run-LED (green).

Positioned to "*MRes*" ("*Modul Reset*"), the Run/Stop switch allows for local deletion of a PLC program from the PLCcore-9G20. This might for example be necessary if an error occurs and the PLC program is running an infinite loop and consequently, accessing the *OpenPCS* programming environment is no longer possible. The procedure for deleting a PLC program is described in section 6.8.

#### 6.7.2 Run-LED (green)

The module connection "/Run-LED" (see Table 5 and reference design in Appendix B) is designed for connecting a Run-LED. This Run-LED provides information about the activity state of the control system. The activity state is shown through different modes:

| © SYS TEC electronic GmbH 2010 | L-1254e 1 | Page 22  |  |

|--------------------------------|-----------|----------|--|

|                                | L-12046_1 | 1 aye 22 |  |

| Table 11: Display status of the Run-LED |

|-----------------------------------------|

|-----------------------------------------|

| LED Mode                                | PLC Activity State                                                                                                                                                |

|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Off                                     | The PLC is in state "Stop":                                                                                                                                       |

|                                         | <ul> <li>the PLC does not have a valid program,</li> </ul>                                                                                                        |

|                                         | <ul> <li>the PLC has received a stop command from the OpenPCS programming<br/>environment or</li> </ul>                                                           |

|                                         | the execution of the program has been canceled due to an internal error                                                                                           |

| Quick flashing in                       | The PLC is on standby but is not yet executing:                                                                                                                   |

| relation 1:8 to pulse                   | <ul> <li>The PLC has received a start command from the OpenPCS programming<br/>environment but the local Run/Stop switch is still positioned to "Stop"</li> </ul> |

| Slow flashing in relation 1:1 to pulse  | The PLC is in state "Run" and executes the PLC program.                                                                                                           |

| Quick flashing in relation 1:1 to pulse | The PLC is in mode "Reset", compare section 6.8                                                                                                                   |

### 6.7.3 Error-LED (red)

Module connection "/*Error-LED*" (see Table 5 and reference design in Appendix B) is designed for connecting an Error-LED. This Error-LED provides information about the error state of the control system. The error state is represented through different modes:

Table 12: Display status of the Error-LED

| LED Mode                                | PLC Error State                                                                                                                                                                                                                                             |

|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Off                                     | No error has occurred; the PLC is in normal state.                                                                                                                                                                                                          |

| Permanent light                         | A severe error has occurred:                                                                                                                                                                                                                                |

|                                         | • The PLC was started using an invalid configuration (e.g. CAN node address 0x00) and had to be stopped or                                                                                                                                                  |

|                                         | • A severe error occurred during the execution of the program and caused the PLC to independently stop its state "Run" (division by zero, invalid Array access,), see below                                                                                 |

| Slow flashing in relation 1:1 to pulse  | A network error occurred during communication to the programming system; the execution of a running program is continued. This error state will be reset independently by the PLC as soon as further communication to the programming system is successful. |

| Quick flashing in relation 1:1 to pulse | The PLC is in mode "Reset", compare section 6.8.                                                                                                                                                                                                            |

| Quick flashing in relation 1:8 to pulse | The PLC is on standby, but is not yet running:                                                                                                                                                                                                              |

|                                         | <ul> <li>The PLC has received a start command from the OpenPCS programming<br/>environment but the local Run/Stop switch is positioned to "Stop"</li> </ul>                                                                                                 |

In case of severe system errors such as division by zero of invalid Array access, the control system passes itself from state "*Run*" into state "*Stop*". This is recognizable by the permanent light of the

| © SYS TEC electronic GmbH 2010 | L-1254e 1 | Page 23          |  |

|--------------------------------|-----------|------------------|--|

|                                | L 12010_1 | 1 ago <u>-</u> o |  |

Error-LED (red). In this case, the error cause is saved by the PLC and is transferred to the computer and shown upon next power-on.

## 6.8 Local deletion of a PLC program

If the Run/Stop switch is positioned to "*MRes*" ("*Modul Reset*") (see section 6.7.1), it is possible to delete a program from the PLCcore-9G20. This might for example be necessary if an error occurs and the PLC program is running an infinite loop and consequently, accessing the *OpenPCS* programming environment is no longer possible. To prevent deleting a PLC program by mistake, it is necessary to keep to the following order:

- (1) Position the Run/Stop switch to "MRes"

- Reset the PLCcore-9G20 (by pressing the reset pushbutton of the Development Board or through temporary power interrupt)

⇒ Run-LED (green) is flashing quickly in relation 1:1 to the pulse

- (3) Position the Run/Stop switch to "Run"

⇒ Error-LED (red) is flashing quickly in relation 1:1 to the pulse

- (4) Reposition Run/Stop switch back to "MRes" within 2 seconds

⇒ PLCcore-9G20 is deleting PLC program

⇒ Run-LED (green) and Error-LED (red) are both flashing alternately

- (5) Reposition Run/Stop switch to "*Stop*" or "*Run*" and reset again to start the PLCcore-9G20 and bring it into normal working state

If Reset of the PLCcore-9G20 is activated (e.g. through temporary power interrupt) while at the same time the Run/Stop switch is positioned to "*MRes*", the module recognizes a reset requirement. This is visible through quick flashing of the Run-LED (green). This mode can be stopped without risk. Therefore, the Run/Stop switch must be positioned to "*Run*" or "*Stop*" (Error-LED is flashing) and it must be waited for 2 seconds. The PLCcore-9G20 independently stops the reset process after 2 seconds and starts a normal working state with the PLC program which was saved last.

## 6.9 Using CANopen for CAN interfaces

The PLCcore-9G20 features 1 CAN interface (CAN0), usable as CANopen Manager (conform to CiA Draft Standard 302). The configuration of this interface (active/inactive, node number, Bitrate, Master on/off) is described in section 7.4.

The CAN interface allow for data exchange with other devices via network variables and is usable from a PLC program via function blocks of type "CAN\_Xxx". More details are included in "User Manual CANopen Extension for IEC 61131-3", Manual no.: L-1008.

The CANopen services **PDO** (*P*rocess *D*ata *O*bjects) and **SDO** (*S*ervice *D*ata *O*bjects) are two separate mechanisms for data exchange between single field bus devices. Process data sent from a node (**PDO**) are available as broadcast to interested receivers. PDOs are limited to 1 CAN telegram and therewith to 8 Byte user data maximum because PDOs are executed as non-receipt broadcast messages. On the contrary, **SDO** transfers are based on logical point-to-point connections ("Peer to Peer") between two nodes and allow the receipted exchange of data packages that may be larger than 8 Bytes. Those data packages are transferred internally via an appropriate amount of CAN telegrams. Both services are applicable for interface CAN0 as well as for CAN1 of the PLCcore-9G20.

| © SYS TEC electronic GmbH 2010 | L-1254e_1 | Page 24 |  |

|--------------------------------|-----------|---------|--|

|--------------------------------|-----------|---------|--|

SDO communication basically takes place via function blocks of type "CAN\_SDO\_Xxx" (see "User Manual CANopen Extension for IEC 61131-3", Manual no.: L-1008). Function blocks are also available for PDOs ("CAN\_PDO\_Xxx"). Those should only be used for particular cases in order to also activate non-CANopen-conform devices. For the application of PDO function blocks, the CANopen configuration must be known in detail. The reason for this is that the PDO function blocks only use 8 Bytes as input/output parameter, but the assignment of those Bytes to process data is subject to the user.

Instead of PDO function blocks, network variables should mainly be used for PDO-based data exchange. Network variables represent the easiest way of data exchange with other CANopen nodes. Accessing network variables within a PLC program takes place in the same way as accessing internal, local variables of the PLC. Hence, for PLC programmers it is not of importance if e.g. an input variable is allocated to a local input of the control or if it represents the input of a decentralized extension module. The application of network variables is based on the integration of DCF files that are generated by an appropriate CANopen configurator. On the one hand, DCF files describe communication parameters of any device (CAN Identifier, etc.) and on the other hand, they allocate network variables to the Bytes of a CAN telegram (mapping). The application of network variables only requires basic knowledge about CANopen.

In a CANopen network, exchanging PDOs only takes place in status "OPERATIONAL". If the PLCcore-9G20 is not in this status, it does not process PDOs (neither for send-site nor for receivesite) and consequently, it does not update the content of network variables. The CANopen Manager is in charge of setting the operational status "OPERATIONAL", "PRE-OPERATIONAL" etc. (mostly also called "CANopen Master"). In typical CANopen networks, a programmable node in the form of a PLC is used as CANopen-Manager. The PLCcore-9G20 is optionally able to take over tasks of the CANopen Manager. How the Manager is activated is described in section 7.4.

As CANopen Manager, the PLCcore-9G20 is able to parameterize the CANopen I/O devices ("CANopen-Slaves") that are connected to the CAN bus. Therefore, upon system start via SDO it transfers DCF files generated by the CANopen configurator to the respective nodes.

#### 6.9.1 CAN interface CAN0

Interface CAN0 features a dynamic object dictionary. This implicates that after activating the PLC, the interface does not provide communication objects for data exchange with other devices. After downloading a PLC program (or its reload from the non-volatile storage after power-on), the required communication objects are dynamically generated according to the DCF file which is integrated in the PLC project. Thus, CAN interface CAN0 is extremely flexible and also applicable for larger amount of data.

For the PLC program, all network variables are declared as "VAR\_EXTERNAL" according to IEC61131-3. Hence, they are marked as "outside of the control", e.g.:

```

VAR_EXTERNAL

NetVar1 : BYTE ;

NetVar2 : UINT ;

END_VAR

```

A detailed procedure about the integration of DCF files into the PLC project and about the declaration of network variables is provided in manual *"User Manual CANopen Extension for IEC 61131-3"* (Manual no.: L-1008).

When using CAN interface CAN0 it must be paid attention that the generation of required objects takes place upon each system start. This is due to the dynamic object directory. "Design instructions" are included in the DCF file that is integrated in the PLC project. **Hence, changes to the configuration can only be made by modifying the DCF file.** This implies that after the network configuration is changed (modification of DCF file), the PLC project must again be translated and loaded onto the PLCcore-9G20.

| © SYS TEC electronic GmbH 2010 | L-1254e_1 | Page 25 |  |

|--------------------------------|-----------|---------|--|

|--------------------------------|-----------|---------|--|

#### 6.9.2 Additional CAN interfaces

In general, the PLC firmware used for PLCcore-9G20 is able to simultaneously operate several CAN interfaces (like other PLC types such as the PLCcore-5484 or PLCmodule-C32).

If necessary, more CAN interfaces can be connected to the module externally. Please contact our support employee if you are interested in this option:

support@systec-electronic.com

# 7 Configuration and Administration of the PLCcore-9G20

### 7.1 System requirements and necessary software tools

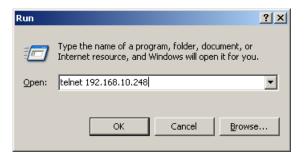

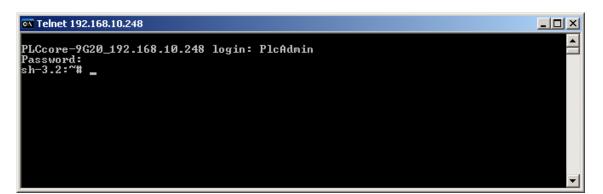

The administration of the PLCcore-9G20 requires any Windows or Linux computer that has available an Ethernet interface and a serial interface (RS232). As alternative solution to the on-board serial interface, SYS TEC offers a USB-RS232 Adapter Cable (order number 3234000, see section 4.4.1) that provides an appropriate RS232 interface via USB port.

All examples referred to in this manual are based on an administration of the PLCcore-9G20 using a Windows computer. Procedures using a Linux computer would be analogous.

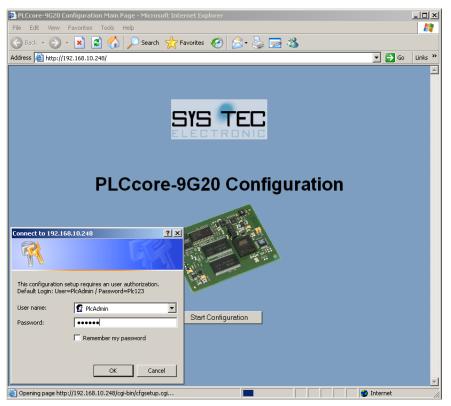

To administrate the PLCcore-9G20 the following software tools are necessary: